## EE420 Lab - Week 4

#### 25th April 2005

### 1 Overview

For the next few weeks, we will be building the parts of an op-amp, then combining them to actually make an op-amp. Build it carefully because you will hopefully use it for the rest of the term.

- Week 4 Differential pair. We build and test a differential amplifier. You get a bonus point for each resistor you can eliminate by using current mirrors.

- Week 5 Adding a second voltage gain stage. One more transistor converts the diff-amp to an op-amp. We will use a PNP. You get a bonus for using a current mirror. This simple op-amp can't drive much of a load, but it should work.

- Week 6 Class-B power stage. We will use some bigger transistors to build a power stage. Then we will add it to our op-amp. If all goes well, you should be able to get a few watts out of it.

- Week 7 High frequency performance. We will experiment with frequency compensation of our op-amp. The goal is to try for the best slew rate and gain-bandwidth product that we can get.

- Week\_8 Active filter. We will build 3 variants of a one op-amp bandpass filter, and characterize them. There is a bonus if you use your op-amp, and it actually works.

- Week 9 Comparitors and Schmitt triggers. We will use the op-amp as a comparitor, and build a Schmitt trigger circuit, and a square wave oscillator. There is a bonus if you use your op-amp, and it actually works.

- Week\_10 Sine wave oscillator. We will use the op-amp to build a Wein bridge or Phase shift sine wave oscillator. There is a bonus if you use your op-amp, and it actually works.

## 2 Objectives - week 4

- 1. To confirm the DC and AC characteristics of differential amplifiers.

- 2. To measure the differential input resistance, differential gain, and common-mode gain of a diff amp.

- 3. To compare the characteristics of a resistor biased amplifier to a current source biased amplifier.

## 3 Background

In this experiment, we will explore the characteristics of a BJT differential pair (emitter coupled pair). This configuration is a major building block for multistage integrated circuit amplifiers. IC's use closely matched pairs, fabricated near each other on the same chip. We will use the LM3046 matched transistor array. The data sheet is attached.

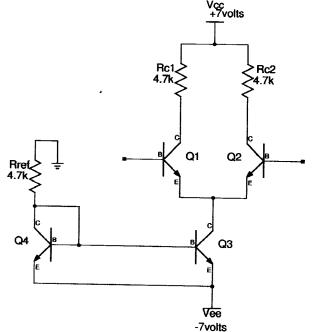

Here is the amplifier:

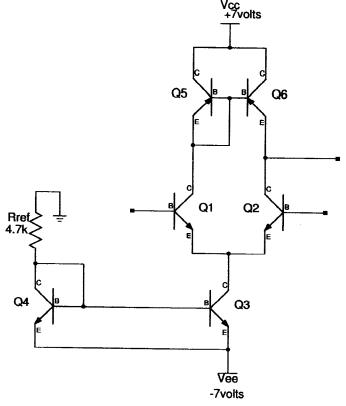

For extra credit, do it again with a current source in place of the emitter resistor:

For still more extra credit, do it again with a current mirror as the collector load:

# 4 Analysis (pre-lab)

### 4.1 Manual analysis

1. Perform a DC bias point analysis of the amplifier. Assume  $\beta = \infty$ ,  $V_{BE} = .7$  then set  $V_{B1} = V_{B2} = 0$ . Determine the values of all currents and voltages.

| 7.7   | The second secon | riches and voltages. |       |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------|

| $V_E$ | $\mid V_C$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | $I_{EE}$             | $I_C$ |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      | 1-0   |

| 1     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |       |

|       | t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | i i                  | 1 1   |

2. Calculate the values of the small signal parameters at the calculated bias point.

|       |           |             | parameters | OF THE C |

|-------|-----------|-------------|------------|----------|

| $g_m$ | $r_{\pi}$ |             | $r_e$      |          |

|       | 1         | <del></del> |            |          |

|       |           | •           |            |          |

#### 3. Calculate:

- (a) The differential input resistance  $r_{id}=v_{id}/i_b$

- (b) The single-ended differential gain  $A_{d(se)} = v_{o2}/v_{id}$

- (c) The differential-output, differential gain  $A_d = v_{od}/v_{id}$

- (d) The single-ended common-mode gain  $A_{cm(se)} = v_{o2}/v_{icm}$

|          |         |          | 27 00111 |

|----------|---------|----------|----------|

| $r_{id}$ | A 4()   | 4.       | 1        |

|          | ^1d(se) | 21d      | Acm(se)  |

|          |         |          |          |

|          | 1       |          |          |

|          |         | <u>.</u> |          |

### 4.2 Simulation

Using a simulator, verify the results you calculated. Check it for beta of 40, 100, and 200.

### 4.3 Current mirror bias (extra credit)

Replace  $R_E$  with the current mirror circuit, and repeat the analysis and simulation. Assume the Early voltage  $V_A = 60$ .

## 4.4 Current mirror load (more extra credit)

Replace  $R_{C1}$  and  $R_{C2}$  with a current mirror circuit, and repeat the analysis and simulation.

## 5 Experiment

- 1. Assemble the circuit as shown in the schematic. Use Q1 and Q2 for the diff-amp. Use the DVM to measure the 4.7k resistors. Choose  $R_{C1}$  and  $R_{C2}$  that are matched within 1% of each other. The actual value is not critical. The matching is critical. Make sure to connect the substrate (pin 13) to the negative supply rail. Lay it out as neatly as you can, using short leads. It should last through the term.

- 2. Connect both bases to ground and measure the quiescent voltages and currents. Verify that  $V_{C1}$  and  $V_{C2}$  are nearly equal. From the measured DC bias point, calculate the values for  $q_{C2}$

| VE       | $V_{C1}$        | $V_{C2}$ | $I_{EE}$           | $I_{C1}$ | $I_{C2}$ |

|----------|-----------------|----------|--------------------|----------|----------|

| $g_{m1}$ | g <sub>m2</sub> | avg      | $\overline{(g_m)}$ | 1        |          |

3. Use a voltage divider network in conjunction with your function generator to produce approximately 10 mV peak-to-peak triangular waveform at 1 kHz. Ground the base of  $Q_2$  and apply the input signal to the base of  $Q_1.(v_{id} = v_{i1} - v_{i2} = v_{i1})$  Measure the value of  $v_{o2}$  and enter the values of  $v_{id}$  and  $v_{o2(d)}$  in the table. Calculate the gain. When using the oscilloscope, you may find it useful to use AC coupling, and set the bandwidth to 20 MHz. For best accuracy, you should set the scope so that the waveform nearly fills the screen.

| $v_{id}$ | $v_{o2(d)}$ | $A_{d(se)}$ |  |

|----------|-------------|-------------|--|

|          |             |             |  |

4. Insert a 2.7k resistor in series with each transistor base lead (a total of 5.4k differential source resistance) and note the decrease on output level. From this, calculate the input resistance.

|          |                 |          | , contraction |

|----------|-----------------|----------|---------------|

| $v_{id}$ | $v_{o2(d.R_s)}$ | $R_{id}$ |               |

|          |                 |          |               |

| L        |                 |          |               |

5. Remove the voltage divider network and increase the amplitude of the function generator to approximately 2 volts peak to peak. Connect both bases together to the function generator.  $(v_{i1}=v_{i2}=v_{icm})$  Measure the value of  $v_{o2}$ , calculate the gain, and enter the values in the table.

| $v_{icm}$ | $v_{o2(cm)}$ | $A_{cm(se)}$ |

|-----------|--------------|--------------|

|           |              |              |

6. Compare your results to what you predicted.

#### 5.1 Extra credit

- 1. Do it again with a current source in place of the emitter resistor.

- 2. For more extra credit, do it again with a current mirror in place of the collector resistors.

## 6 Report

# 6.1 Executive summary (on cover)

Show a schematic of the amplifier you measured, with its measurements in a table. If you did any extra credit options, show the schematic of the best amplifier, and the measurements for all of them.

## 6.2 More detailed summary

Write a paragraph on what you learned, and point out any surprises. Does it match the simulation? Explain. For the basic experiment, limit this section to one page. If you did any extra credit options, you may use two pages if you need it.

### 6.3 Journal

Provide a journal of what you did, with enough detail that someone else can reproduce your experiment and verify your work.

## 6.4 Simulation and analysis

If your results differ significantly from the simulation or analysis, try to find out why. Rerun the simulation if you need to.

## 7 Grading

For the basic experiment, the grade will be calculated according to the 10 point checklist.

If you did any extra credit options, extra points will be added as follows:

Up to 3 points (1 for the preliminary analysis, 1 for the experiment, 1 for the final report) will be added for the emitter current source.

Up to 6 points (2 for the preliminary analysis, 2 for the experiment, 2 for the final report) will be added for the current mirror load. This option requires significant extra work.

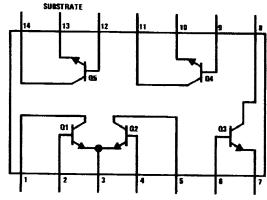

# LM3045/LM3046/LM3086 Transistor Arrays

#### **General Description**

The LM3045, LM3046 and LM3086 each consist of five general purpose silicon NPN transistors on a common monolithic substrate. Two of the transistors are internally connected to form a differentially-connected pair. The transistors are well suited to a wide variety of applications in low power system in the DC through VHF range. They may be used as discrete transistors in conventional circuits however, in addition, they provide the very significant inherent integrated circuit advantages of close electrical and thermal matching. The LM3045 is supplied in a 14-lead cavity dual-in-line package rated for operation over the full military temperature range. The LM3046 and LM3086 are electrically identical to the LM3045 but are supplied in a 14-lead molded dual-in-line package for applications requiring only a limited temperature range.

#### **Features**

- Two matched pairs of transistors

V<sub>BE</sub> matched ±5 mV

Input offset current 2 μA max at I<sub>C</sub> = 1 mA

- Five general purpose monolithic transistors

- Operation from DC to 120 MHz

- Wide operating current range

- Low noise figure

3.2 dB typ at 1 kHz

■ Full military

temperature range (LM3045)

-55°C to +125°C

#### **Applications**

- General use in all types of signal processing systems operating anywhere in the frequency range from DC to VHF

- Custom designed differential amplifiers

- Temperature compensated amplifiers

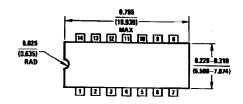

### **Schematic and Connection Diagram**

#### Dual-In-Line and Small Outline Packages

TL/H/7950-1

Top View

Order Number LM3045J, LM3046M, LM3046N or LM3086N

See NS Package Number J14A, M14A or N14A

### Absolute Maximum Ratings (T<sub>A</sub> = 25°C)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| Distributors for availability and specifications. | LM3                | 045              | LM3046/            |                  |       |

|---------------------------------------------------|--------------------|------------------|--------------------|------------------|-------|

|                                                   | Each<br>Transistor | Total<br>Package | Each<br>Transistor | Total<br>Package | Units |

| Power Dissipation:                                |                    | •                |                    | _                |       |

| $T_A = 25^{\circ}C$                               | 300                | 750              | 300                | 750              | mW    |

| $T_A = 25^{\circ}C$ to 55°C                       |                    |                  | 300                | 750              | mW    |

| T <sub>A</sub> > 55℃                              |                    |                  | Derate             | at 6.67          | mW/℃  |

| $T_A = 25^{\circ}C$ to 75°C                       | 300                | 750              |                    |                  | mW    |

| T <sub>A</sub> > 75℃                              | Derate             | e at 8           |                    |                  | mW/°C |

| Collector to Emitter Voltage, V <sub>CEO</sub>    | 15                 |                  | 15                 |                  | V     |

| Collector to Base Voltage, V <sub>CBO</sub>       | 20                 |                  | 20                 |                  | ٧     |

| Collector to Substrate Voltage, VCIO (Note 1)     | 20                 |                  | 20                 |                  | ٧     |

| Emitter to Base Voltage, V <sub>EBO</sub>         | 5                  |                  | 5                  |                  | ٧     |

| Collector Current, IC                             | 50                 |                  | 50                 |                  | mA    |

| Operating Temperature Range                       | −55°C to           | +125°C           | - 40°C to          | +85°C            |       |

| Storage Temperature Range                         | −65°C to           | +150°C           | − <b>65°</b> C to  | + 85°C           |       |

| Soldering Information                             |                    |                  |                    |                  |       |

| Dual-In-Line Package Soldering (10 Sec.)          | 260°C              |                  | 260°C              |                  |       |

| Small Outline Package                             |                    |                  |                    |                  |       |

| Vapor Phase (60 Seconds)                          |                    |                  | 215°C              |                  |       |

| Infrared (15 Seconds)                             |                    |                  | 220°C              |                  |       |

See AN-450 "Surface Mounting Methods and Their Effect on Product Reliability" for other methods of soldering surface mount devices.

### Electrical Characteristics (T<sub>A</sub> = 25°C unless otherwise specified)

|                                                                                                             |                                                                                                                                                        | Limits |                |             | Limits |        |     |       |

|-------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------|-------------|--------|--------|-----|-------|

| Parameter                                                                                                   | Conditions                                                                                                                                             | LM:    | LM3045, LM3046 |             |        | LM3086 | 3   | Units |

|                                                                                                             |                                                                                                                                                        | Min    | Тур            | Max         | Min    | Тур    | Max |       |

| Collector to Base Breakdown Voltage (V(BR)CBO)                                                              | $I_{C} = 10  \mu A, I_{E} = 0$                                                                                                                         | 20     | 60             |             | 20     | 60     |     | ٧     |

| Collector to Emitter Breakdown Voltage (V(BR)CEO)                                                           | $I_C = 1$ mA, $I_B = 0$                                                                                                                                | 15     | 24             |             | 15     | 24     |     | ٧     |

| Collector to Substrate Breakdown<br>Voltage (V(BR)CIO)                                                      | $I_{C} = 10  \mu A$ , $I_{CI} = 0$                                                                                                                     | 20     | 60             |             | 20     | 60     |     | ٧     |

| Emitter to Base Breakdown Voltage (V(BR)EBO)                                                                | le 10 μA, lc = 0                                                                                                                                       | 5      | 7              |             | 5      | 7      |     | ٧     |

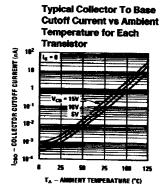

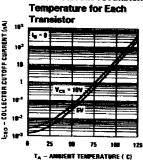

| Collector Cutoff Current (I <sub>CBO</sub> )                                                                | V <sub>CB</sub> = 10V, I <sub>E</sub> = 0                                                                                                              |        | 0.002          | 40          |        | 0.002  | 100 | nA    |

| Collector Cutoff Current (I <sub>CEO</sub> )                                                                | V <sub>CE</sub> = 10V, I <sub>B</sub> = 0                                                                                                              |        |                | 0.5         |        |        | 5   | μΑ    |

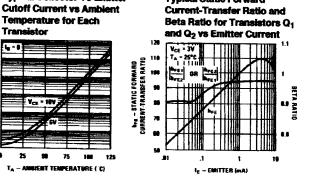

| Static Forward Current Transfer                                                                             | $\label{eq:VCE} \begin{array}{l} \text{VCE} = 3\text{V} \\ \text{I}_{\text{C}} = 10 \text{ mA} \\ \text{I}_{\text{C}} = 10 \mu\text{A} \\ \end{array}$ |        | 100            |             |        | 100    |     |       |

| Ratio (Static Beta) (hFE)                                                                                   |                                                                                                                                                        | 40     | 100            |             | 40     | 100    |     |       |

|                                                                                                             | lc = 10 μA                                                                                                                                             |        | 54             | · · · · · · |        | 54     |     |       |

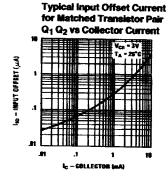

| Input Offset Current for Matched Pair Q <sub>1</sub> and Q <sub>2</sub>  I <sub>O1</sub> - I <sub>IO2</sub> | V <sub>CE</sub> = 3V, I <sub>C</sub> = 1 mA                                                                                                            |        | 0.3            | 2           |        |        |     | μΑ    |

| Base to Emitter Voltage (V <sub>BE</sub> )                                                                  | V <sub>CE</sub> = 3V (I <sub>E</sub> = 1 mA                                                                                                            | -      | 0.715          |             |        | 0.715  |     |       |

|                                                                                                             | $V_{CE} = 3V$ $\begin{cases} I_E = 1 \text{ mA} \\ I_E = 10 \text{ mA} \end{cases}$                                                                    |        | 0.800          |             |        | 0.800  |     | ٧     |

| Magnitude of Input Offset Voltage for<br>Differential Pair  V <sub>BE1</sub> - V <sub>BE2</sub>             | V <sub>CE</sub> = 3V, I <sub>C</sub> = 1 mA                                                                                                            |        | 0.45           | 5           |        |        |     | mV    |

| Magnitude of Input Offset Voltage for Isolated Transistors  VBE3 - VBE4 ,  VBE4 - VBE5 ,  VBE5 - VBE3       | V <sub>CE</sub> = 3V, I <sub>C</sub> = 1 mA                                                                                                            |        | 0.45           | 5           |        |        |     | mV    |

| Temperature Coefficient of Base to Emitter Voltage $\left(\frac{\Delta V_{BE}}{\Delta T}\right)$            | V <sub>CE</sub> = 3V, I <sub>C</sub> = 1 mA                                                                                                            |        | -1.9           |             |        | 1.9    |     | mV/°C |

| Collector to Emitter Saturation Voltage (V <sub>CE(SAT)</sub> )                                             | I <sub>B</sub> = 1 mA, I <sub>C</sub> = 10 mA                                                                                                          |        | 0.23           |             |        | 0.23   |     | ٧     |

| Temperature Coefficient of Input Offset Voltage $\left( \frac{\Delta V_{10}}{\Delta T} \right)$             | V <sub>CE</sub> = 3V, I <sub>C</sub> = 1 mA                                                                                                            |        | 1.1            |             |        |        |     | μV/°C |

Note 1: The collector of each transistor of the LM3045, LM3046, and LM3086 is isolated from the substrate by an integral diode. The substrate (terminal 13) must be connected to the most negative point in the external circuit to maintain isolation between transistors and to provide for normal transistor action.

| Parameter                                         | Conditions                                                                            | Min  | Тур                              | Max | Units |

|---------------------------------------------------|---------------------------------------------------------------------------------------|------|----------------------------------|-----|-------|

| Low Frequency Noise Figure (NF)                   | $f = 1 \text{ kHz}, V_{CE} = 3V,$<br>$I_C = 100 \mu\text{A}, R_S = 1 \text{ k}\Omega$ |      | 3.25                             |     | dB    |

| LOW FREQUENCY, SMALL SIGNAL EQUIVALEN             | IT CIRCUIT CHARACTERIS                                                                | TICS |                                  |     | L     |

| Forward Current Transfer Ratio (h <sub>fe</sub> ) | f = 1 kHz, V <sub>CE</sub> = 3V,<br>I <sub>C</sub> = 1 mA                             |      | 110 (LM3045, LM3046)<br>(LM3086) |     |       |

| Short Circuit Input Impednace (hie)               |                                                                                       |      | 3.5                              |     | kΩ    |

| Open Circuit Output Impedance (hoe)               |                                                                                       |      | 15.6                             |     | μmho  |

| Open Circuit Reverse Voltage Transfer Ratio (hre) |                                                                                       |      | 1.8 x 10 <sup>-4</sup>           |     |       |

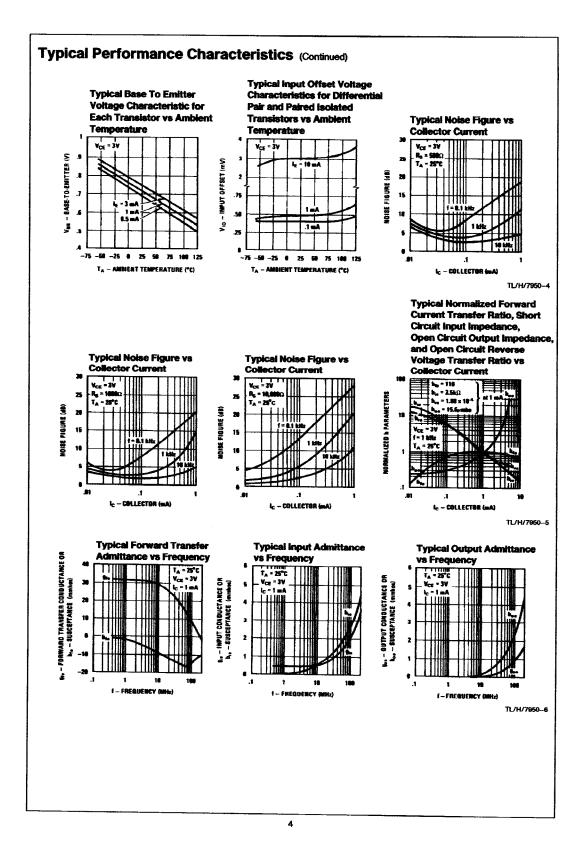

| ADMITTANCE CHARACTERISTICS                        |                                                                                       |      |                                  |     |       |

| Forward Transfer Admittance (Yfe)                 | f = 1 MHz, V <sub>CE</sub> = 3V,                                                      |      | 31 – j 1.5                       |     |       |

| Input Admittance (Y <sub>le</sub> )               | I <sub>C</sub> = 1 mA                                                                 |      | 0.3+J0.04                        |     |       |

| Output Admittance (Yoe)                           |                                                                                       |      | 0.001+j0.03                      |     |       |

| Reverse Transfer Admittance (Yre)                 |                                                                                       |      | See Curve                        |     |       |

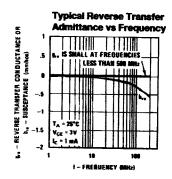

| Gain Bandwidth Product (fT)                       | $V_{CE} = 3V$ , $I_{C} = 3 \text{ mA}$                                                | 300  | 550                              |     |       |

| Emitter to Base Capacitance (CEB)                 | V <sub>EB</sub> = 3V, I <sub>E</sub> = 0                                              |      | 0.6                              |     | pF    |

| Collector to Base Capacitance (CCB)               | $V_{CB} = 3V$ , $I_C = 0$                                                             |      | 0.58                             |     | pF    |

| Collector to Substrate Capacitance (CCI)          | $V_{CS} = 3V, I_{C} = 0$                                                              |      | 2.8                              |     | ρF    |

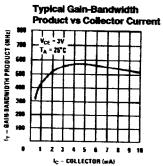

## **Typical Performance Characteristics**

**Typical Collector To Emitter**

**Typical Static Forward**

TL/H/7950-2

**Typical Static Base To Emitter**

TL/H/7950-3

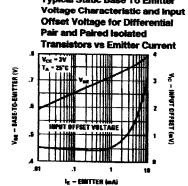

# **Typical Performance Characteristics** (Continued)

TL/H/7950-7

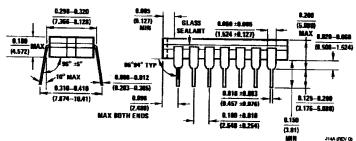

# Physical Dimensions inches (millimeters)

Ceramic Dual-In-Line Package (J) Order Number LM3045J NS Package Number J14A